在线网址纳米压印本领与ASML熟谙的EUV光刻本领比较-九游娱乐(中国)有限公司-官方网站

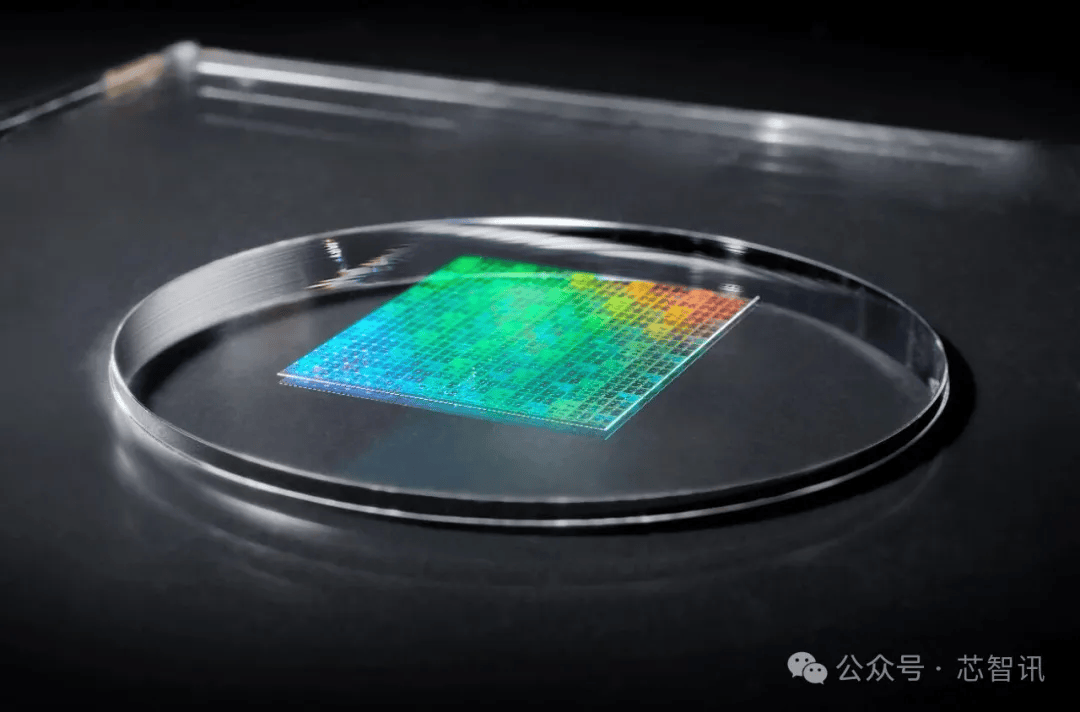

近日,日本印刷株式会社(DNP)晓示,顺利开发出电阶梯宽仅为10nm的纳米压印(NIL)光刻模板,可用于很是于1.4纳米等第的逻辑半导体电路图形化,不错欢快智妙手机、数据中心以及NAND闪存等拓荒中使用的顶端逻辑半导体的微型化需求。该居品将在 2025 年 12 月 17 日至 19 日在东京海外展览中心 (Tokyo Big Sight) 举行的日本海外半导体展 (SEMICON Japan 2025) 上展出。

比年来,跟着群众关于算力需求的捏续提高,顶端半导体微型化的需求也日益增长,这也推动了基于极紫外(EUV)光刻本领的芯片坐褥正在抵制发展。商酌词,由于EUV光刻拓荒本钱不菲(单台本钱高达1.5亿好意思元),这也使得坐褥线诞生本钱愈加不菲,况兼曝光过程能耗也强横常高,因此垂危需要裁减制形本钱并减少对环境的影响的处置决议。

因此,在光刻机阛阓与ASML竞争溃逃的日本厂商佳能(Canon)近十多年来一直在与日本光罩等半导体零组件制造商大日本印刷株式会社(DNP)勾通研发纳米压印工艺。

所谓纳米压印本领,并不是哄骗传统的光学图像投影的旨趣将集成电路的微不雅结构转机到硅晶圆上,而是更访佛于印刷本领,即顺利通过压印形成图案。在晶圆上只压印1次,就不错在特定的位置形成复杂的2D或3D电路图,不仅至极的简易,还能在无需EUV光刻机辅助的情况下杀青5nm制程的,同期还能极大的裁减拓荒采购本钱及芯片制形本钱。

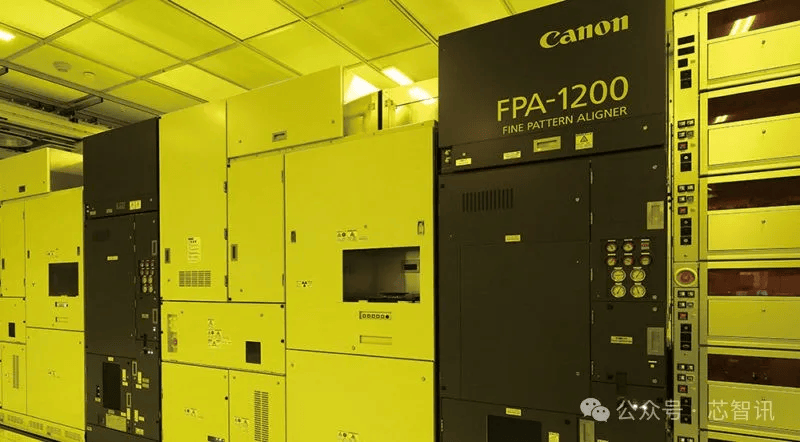

2023年10月,佳能认真发布了基于纳米压印本领(NIL)的芯片制造拓荒FPA-1200NZ2C,为坐褥先进制程芯片开辟出一条本钱更低的全新旅途。

阐述佳能的先容,其纳米压印拓荒不错辅助10nm以下顶端制程的制造,致使不错辅助到5nm制程。相较于面前已商用化的EUV光刻本领,诚然纳米压印本领的芯片制造速率要比传统光刻模式慢,但纳米压印本领可大幅减少约90%的芯片制造的耗能,并拓荒采购本钱也可裁减90%。佳能首席奉行官御手洗富士夫此前就指出,佳能纳米压印拓荒的“价钱将比ASML的EUV光刻机低一位数(即仅有10%)”

不外,即便如斯,纳米压印本领与ASML熟谙的EUV光刻本领比较,竞争力依然相对有限。然则,跟着制程工艺参加到埃米级别,ASML的High NA EUV光刻拓荒将会带来更高的制形本钱,如若纳米压印本领也有时鼓吹到埃米级,那么其竞争力无疑将会进一步突显。

而关于纳米压印本领来说,决定其有时杀青的半导体制程工艺等第,与其纳米压印模板顺利商酌。与光学曝光可放大数倍不同,纳米压印需以1:1的尺寸刻写“主模板→子模板→职责模板”,每一步齐可能产生弱势。关于20nm以下特征尺寸,则需要依赖着手进的多光束电子束写入机(MBMW)辅助,其越顶端的特征尺寸的制造难度、本钱与良率压力权贵。

自2003年以来,DNP公司一直神敢于开发纳米压印光刻(NIL)模板,通过将刻有电路图案的模板顺利压印并转机到基板上,从而裁减曝光过程中的能耗,并积贮了特有的本领决窍。

面前,DNP晓示依然顺利开发出一种10nm线宽的纳米压印光刻(NIL)模板,很是于面前的1.4nm制程,不错替代部分EUV致使High NA EUV工艺,用于制造顶端逻辑半导体,以欢快客户关于本钱终结的需求。通过提供该模板,DNP将拓展客户半导体制造工艺的接收规模,从而裁减制形本钱并减少对环境的影响。

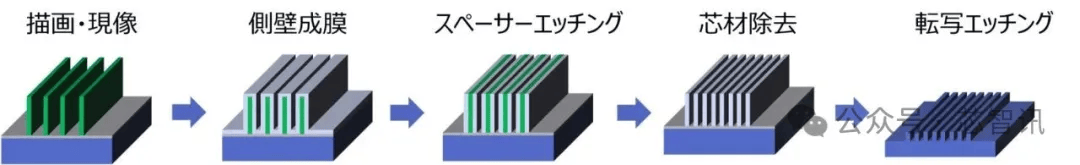

据先容,DNP是哄骗自瞄准双重图案化(SADP)杀青了10nm线宽的纳米压印光刻模板的微型化,该本领通过在光刻系统形成的图案上进行薄膜千里积和蚀刻,从而使图案密度加倍。

△DNP开发了电阶梯宽为 10nm 的纳米压印模板的经过

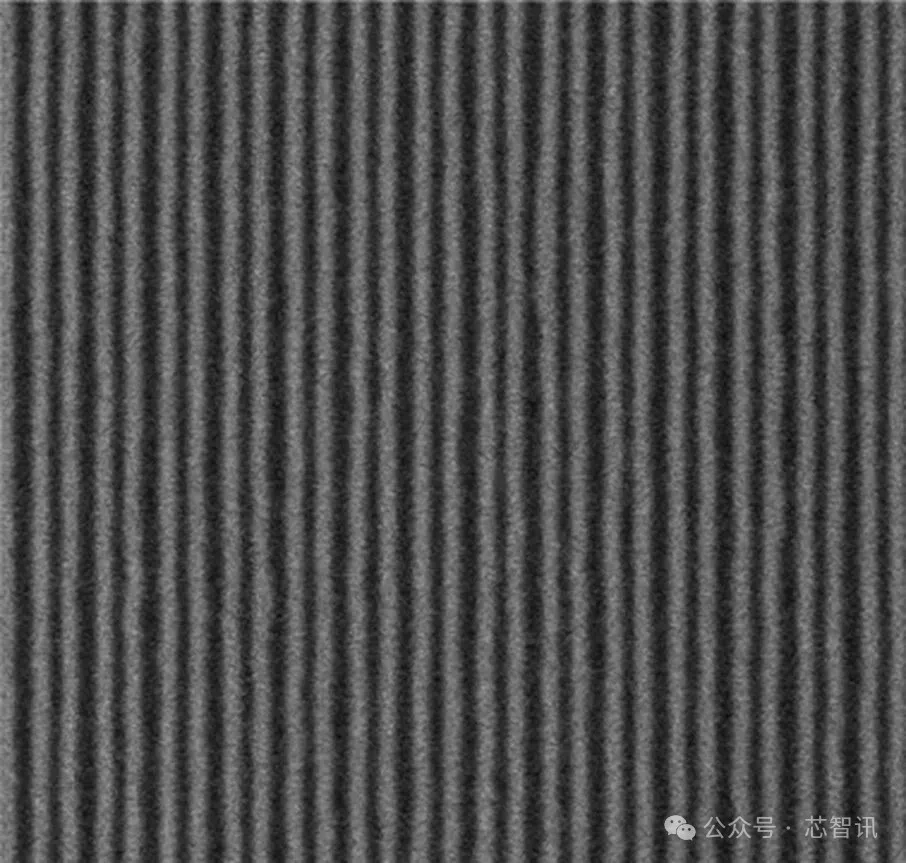

△DNP纳米压印掩模上,线宽为10nm的线

DNP指出,“采选纳米压印光刻本领的超缜密半导体节能工艺”将功耗裁减至传统曝光工艺(举例ArF/浸没式DUV、EUV)的十分之一傍边。

面前,DNP正与半导体制造商和其他客户伸开同样,并已初始对纳米压印光刻(NIL)模板进行评估职责,指标是在2027年头始量产。

瞻望未来,为了进一步杀青半导体微型化和本钱裁减,DNP晓示将连接鼓吹NIL模板的进一步开发,并加强其坐褥系统以欢快抵制增长的需求,指标是在2030财年将NIL销售额提高40亿日元。

裁剪:芯智讯-浪客剑在线网址